This is the peer reviewed version of the following article:

Szczepanski S., Pankiewicz B., Koziel S., Programmable feedforward linearized CMOS OTA for fully differential continuous-time filter design, INTERNATIONAL JOURNAL OF CIRCUIT THEORY AND APPLICATIONS, Vol. 38, Iss. 9 (2010), pp. 885-899

which has been published in final form at <a href="https://doi.org/10.1002/cta.602">https://doi.org/10.1002/cta.602</a>. This article may be used for non-commercial purposes in accordance with Wiley Terms and Conditions for Use of Self-Archived Versions. This article may not be enhanced, enriched or otherwise transformed into a derivative work, without express permission from Wiley or by statutory rights under applicable legislation. Copyright notices must not be removed, obscured or modified. The article must be linked to Wiley's version of record on Wiley Online Library and any embedding, framing or otherwise making available the article or pages thereof by third parties from platforms, services and websites other than Wiley Online Library must be prohibited.

# Programmable Feedforward Linearized CMOS OTA for Fully-Differential Continuous-Time Filter Design

Stanislaw Szczepanski<sup>1</sup>, Bogdan Pankiewicz<sup>2</sup> and Slawomir Koziel<sup>3</sup>

**Abstract.** In this paper, a feedforward linearization method for programmable CMOS Transconductance Operational Amplifier (OTA) is described. The proposed circuit technique is developed using simple source-coupled differential pair transconductors, a feedback-loop amplifier for self-adjusting transcoductance ( $g_m$ ) and a linear reference resistor (R). As a result, an efficient linearization of a transfer characteristic of the OTA is obtained. SPICE simulations show that for 0.35  $\mu$ m AMS CMOS process with a single +3 V power supply, total harmonic distortion (THD) at 1  $V_{pp}$  and temperature range from  $-30^{\circ}$ C to  $+90^{\circ}$ C is less than -49.3 dB in comparison to -35.8 dB without linearization. Moreover the input voltage range of linear operation is increased. Power consumption of the linearized OTA circuit is 0.86 mW. Finally, the OTA is used to design a third-order elliptic low-pass filter in high-frequency range. The cutoff frequency of the Operational Transconductance Amplifier-Capacitor (OTA-C) filter is tunable in the range of 322.6 kHz - 10 MHz using the feedforward linearized OTAs with the digitally programmable current mirrors.

**Index terms:** CMOS OTA, linearized OTA, feedforward linearization, fully-differential OTA.

## 1. INTRODUCTION

Programmable, highly linear CMOS Operational Transconductance Amplifiers (OTAs) with wide dynamic range and excellent high frequency performance are useful building blocks for the design of many analog circuits and mixed signal systems. Applications such as high-frequency continuous-time (CT) analog OTA-C filters provide solutions for various signal processing tasks [1]-[11]. In recent years also the Field Programmable Analog Arrays

Department of Microelectronic Systems, Faculty of Electronics, Telecommunications and Informatics, Gdansk University of Technology, Gdansk, Narutowicza 11/12, 80-952, Poland; e-mail: <a href="mailto:stanisla@eti.pg.gda.pl">stanisla@eti.pg.gda.pl</a>

<sup>&</sup>lt;sup>2</sup> Department of Microelectronic Systems, Faculty of Electronics, Telecommunications and Informatics, Gdansk University of Technology, Gdansk, Narutowicza 11/12, 80-952, Poland; e-mail: <a href="mailto:bpa@ue.eti.pg.gda.pl">bpa@ue.eti.pg.gda.pl</a>

<sup>&</sup>lt;sup>3</sup> School of Science and Engineering, Reykjavík University, Kringlunni 1, IS-103 Reykjavík, Iceland; e-mail:

(FPAAs) based on the tunable (programmable) OTAs and integrating capacitors (C) have been developed sucessfully to built reconfigurable hardware platforms (e.g., for CT analog filter rapid-prototyping) [15]-[21].

One of the simplest and most widely used MOS transconductors for high-frequency operations (e.g., active filters) is a source-coupled differential pair. However, it can be observed that while offering low noise, its large signal characteristics are extremally nonlinear. Therefore, the dynamic range and the efficiency of the differential pair using MOS transistors are limited [5], [12]-[14]. A number of techniques for improving the linear properties of CMOS transconductance elements based on the source-coupled differentional pairs have been proposed [22]-[38]. These techniques employ MOS transistors operating both in saturation in triode regions. Methods such as adapting biasing (e.g., [27]), source degeneration (e.g., [30]), and current differencing/current addition (e.g., [26]) lead to effective linearization. However, the performance improvement is obtained at the expense of the power consumption increase, reduced transcondutance factor as well as the power factor defined here as the maximum linear output current divided by the total bias current [5].

It is well known that an application of the feedforward technique enables us to improve performance of many analog signal processing circuits. For example, this technique is widely used to reduce nonlinear distortion in amplifiers [40]-[48]. Moreover, it is successfully employed to frequency compensation of operational amplifiers (Opamps) and OTAs [49]-[53].

In this work, a novel highly linear programmable CMOS operational transconductance amplifier is proposed. The OTA circuit developed here uses, as basic building blocks, simple differentional-pair transconductors, a reference resistor and digitally programmable current mirrors. The linearization follows by employing an active-error feedforward scheme. The error signal is generated using an additional differential-pair transconductor and a resistor which is assumed to be linear. This resistor can be an external one or it can be implemented as a monolitic element, e.g., using a highly-resistive poly layer.

The proposed technique gives effective linearization and it is free of drawbacks mentioned in the previous paragraph. In particular, it allows us to implement the OTA circuit which has extremely low power consumption, extended linear range operation as well as good transconductance programming (tuning) capability. Moreover, the feedforward linearized OTA offers excellent high frequency performance, which makes the developed circuit suitable for OTA-C filter applications at higher frequencies.

The paper is organized as follows. In Section 2, a description of the proposed feedforward linearization method is presented. In Section 3, the design of the complete circuit of the programmable linearized differential CMOS OTA and its parameter comparison is performed. Section 4 presents the third-order OTA-C elliptic filter design with the simulation results. Section 5 concludes the paper.

## 2. DESCRIPTION OF FEEDFORWARD LINEARIZATION METHOD

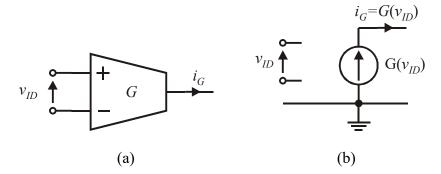

For the purpose of the subsequent analysis, the nonlinear transfer characteristic of the transconductance elements will be characterized using power series expansion. Let  $i_G$  denotes the output current of the transconductor in Fig. 1, and its power series dependence is given by

$$i_G = G[(v_{ID})] = \sum_{n=1}^{\infty} g_n v_{ID}^n(t)$$

(1)

where  $v_{ID}$  is the differential input voltage and the coefficients  $g_n$  are defined as

$$g_{n} = \frac{1}{n!} \frac{d^{n} G[(v_{ID})]}{dv_{ID}^{n}} \bigg|_{v_{ID}=0}$$

(2)

By definition, first-order coefficient  $g_1$  of (2) is the transconductance  $g_m$  of the amplifier.

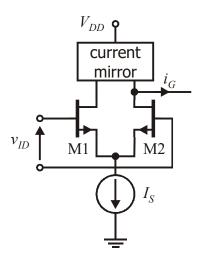

Consider a simple CMOS differential pair transconductor shown in Fig. 2. Using the square-law MOS transistor modeling, its normalized transfer characteristic around zero can be written as follows [12]

$$i(x) = 2I_S x \sqrt{1 - x^2}$$

(3)

where x is a normalized input voltage defined as

$$x = \frac{v_{id}}{2(V_{GS} - V_T)} \tag{4}$$

with  $V_{GS}$  being the quiescent value of the gate-source voltage of both M1 and M2,  $V_T$  being their threshold voltage, and  $I_S$  being the biasing current of the differential pair. Actually, formula (3) is valid for  $|x| \le \sqrt{2}/2$ . For larger x, the transfer characteristic saturates. Then, the corresponding power series expansion of (3) is given by

$$i(x) = 2I_s \left( x - \frac{1}{2} x^3 - \frac{1}{8} x^5 - \frac{1}{16} x^7 - \frac{5}{128} x^9 \cdots \right)$$

(5)

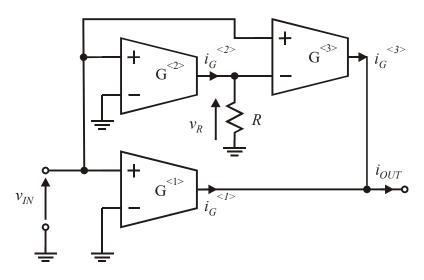

Fig. 3 shows the circuit concept of transconductance amplifier linearization based on active-error feedforward method [49], [53]. Amplifiers G<sup><1></sup>, G<sup><2></sup> and G<sup><3></sup>, modeled as in Fig. 1, are assumed to be identical. Their transfer characteristics are described by the power series expansion (1). Additionally, it is assumed that the resistor R in Fig. 3 is perfectly linear and its resistance is equal to  $1/g_m$ . In practice, e.g., in integrated circuits implementations, some technologies offer high resistive poly which can be used to realize resistor R. Alternatively, such a resistor can be treated as an external (discrete) element.

Using (1), the output current of the overall circuit in Fig. 3 can be written as follows

$$i_{OUT}(t) = \sum_{n=1}^{\infty} g_n v_{IN}^n(t) + \sum_{n=1}^{\infty} g_n [v_{IN}(t) - v_R(t)]^n$$

(6)

where

$$v_{R}(t) = g_{1}^{-1} \sum_{n=1}^{\infty} g_{n} v_{IN}^{n}(t)$$

(7)

This means that the voltage at the input of the transconductor G<sup><3></sup> (working as an error amplifier) is expressed as

$$v_{IN}(t) - v_R(t) = v_{IN}(t) - g_1^{-1} \sum_{n=1}^{\infty} g_n v_{IN}^n(t) = -g_1^{-1} \sum_{n=2}^{\infty} g_n v_{IN}^n(t)$$

(8)

Hence, we obtain

$$i_{OUT}(t) = \sum_{n=1}^{\infty} g_n v_{IN}^n(t) + \sum_{n=1}^{\infty} g_n \left[ -g_1^{-1} \sum_{n=1}^{\infty} g_n v_{IN}^k(t) \right]^n$$

(9)

Normally, the value of  $[v_{IN}(t) - v_R(t)]$  is much smaller than the values of the input voltages of transconductors G<sup><1></sup> and G<sup><2></sup>, which allows us to neglect the higher order terms in the output current of G<sup><3></sup>. This leads to the following approximation

$$i_{OUT}(t) \cong \sum_{n=1}^{\infty} g_n v_{IN}^n(t) - \sum_{n=2}^{\infty} g_n v_{IN}^n(t) = g_1 v_{IN}(t)$$

(10)

which shows the perfect cancellation of nonlinearities of the overall transconductance amplifier in Fig. 3.

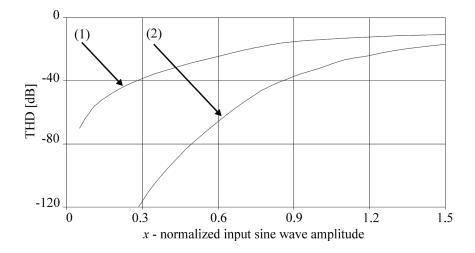

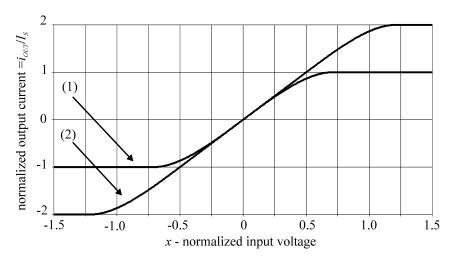

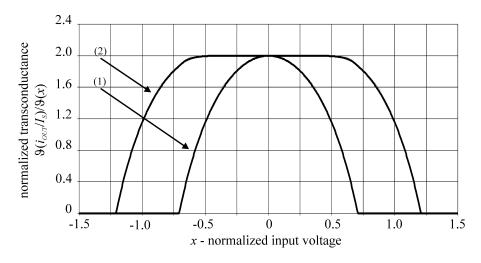

One can calculate THD for both original and linearized circuit assuming the transfer characteristic (3) for all transconductors (in particular, we no longer neglect higher order terms in the output current of G<sup><3></sup> as in (10)). The results of numerical calculations are presented in Figs. 4, 5 and 6. Fig. 4 shows theoretical THD characteristics for the considered circuits. Figs. 5 and 6 show theoretical transfer and transconductance characteristics, respectively. It is worth noting that using the active-error feedforward technique one can obtain not only significant reduction of THD but also considerable increase of linear range of operation (recall that the transfer characteristic for differential pair transconductor saturates for  $x \approx 0.7$ ; for linearized circuit it happens for  $x \approx 1.2$ ).

The proposed OTA (Fig. 3) has a higher linearity range, but due to increased current consumption and devices count noise is also increased compared to the simple differential pair. If we denote  $v^2_{Gnoise}$  as total input referred power spectral density noise of a single

transconductor G from Fig. 3, then the input referred three-block feedforward transconductance amplifier power spectral density noise is equal to:

$$v_{noise}^{2} = 3v_{Gnoise}^{2} + \frac{4kTR}{(g_{m}R)^{2}}\Big|_{R=1/g_{m}} = 3v_{Gnoise}^{2} + 4kTR$$

(11)

where 4kTR is the thermal noise of resistor R, k is the Boltzman's constant, T is the absolute temperature, and R is resistance of resistor which is due to nonlinearity cancellation condition also equal to  $1/G=1/g_m$ .

According to [5], input referred noise of a single MOS pair assuming medium range of frequency can be approximated by:

$$v_{pair\_noise}^2 = \frac{16}{3} kT \frac{1}{g_m}$$

(12)

Using (11) and (12), the noise increase of the linearized transconductance amplifier can be approximated as

$$\frac{v_{noise}^2}{v_{pair noise}^2} = \frac{15}{4} = 3.75 \tag{13}$$

Note that equation (12) is an underestimated approximation of real MOS pair (without taking into account current mirrors noise and body noise), which means that the noise increase given by (13) is overestimated. The actual noise of the amplifier is also slightly smaller because the contribution of other devices (not only the differential pair) to the total noise makes the thermal noise of resistor R less visible for linearized amplifier. In particular, if the resistor noise is assumed to be negligibly small comparison to the noise of a single amplifier G then value of noise ratio would be equal 3. Thus, (13) describes a worst case scenario. The degradation of dynamic range from below for the actual amplifier will be then somewhere between 4.76dB to 5.74dB.

The main advantage of proposed amplifier is its increased linearity comparing to the simple reference CMOS differential pair. As it is shown at the Figs. 4 and 5 input voltage for -40dB THD is 0.86 while for simple pair is 0.27. Thus, dynamic range increases by 10.1dB and thus total dynamic range of the linearized amplifier is at least 4.32dB better than for the amplifier based on simple MOS pair. Linearized amplifier works also better for higher signals and due to this is a good alternative for today needs with continuous decrease of power supply voltages and problems with high amplitude signals processing.

Another general problem concerning CMOS amplifiers is the input referred offset voltage. Since proposed amplifier does not use current differentiation, its performance is not degraded comparing to the simple MOS pair. Moreover, improved linearity makes it usable even at the presence of relatively high mismatches and offsets. Of course, for instrumentation amplifier applications offset have to be cancelled using specialized sub-circuits which are not considered here [55].

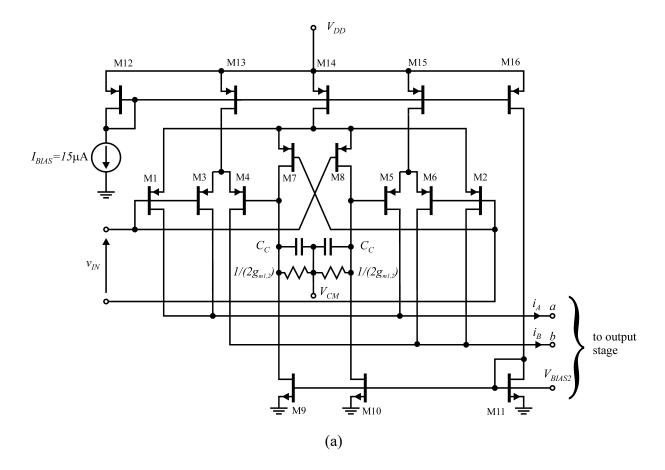

#### 3. PROGRAMMABLE DIFFERENTIAL PAIR CMOS OTA

Fig. 7 shows a programmable fully differential OTA implementation using the active-error feedforward concept discussed in Section 2. The OTA is realized using AMS 0.35µm technology with highly-resistive POLY option. MOS dimensions and resistances are summarized at the end of the section. Resistors were designed using high resistive POLY layer. Note that presented circuit is a differential-input two-output OTA, which follows from the fact that such a circuit configuration is more suitable for filtering applications. Thus, there it is a slight modification of the basic concept presented in Fig. 3. In Fig. 7(a) input stage is presented, which realizes idea from Fig. 3. The transistors M1, M2 and M7, M8 form classical source-coupled differential pairs with current sink realized by transistor M14. Actually, the pair M1 and M2 implements two-output counterpart of transconductor G<sup><1></sup> in Fig. 3. Transistors M7, M8 implement the counterpart of transconductor G<sup><2></sup> loaded by resistor

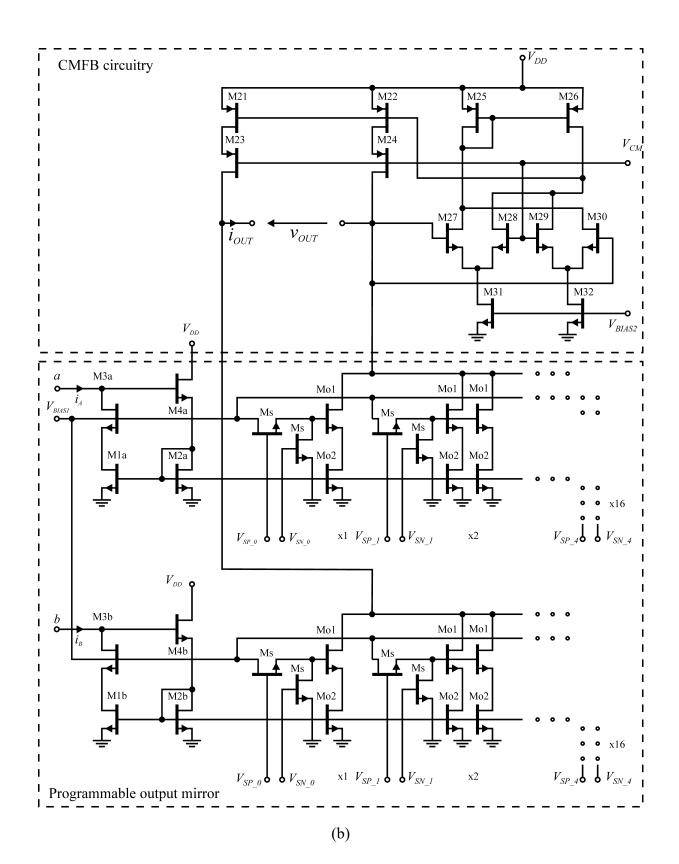

1/2g<sub>m</sub>. Differential pairs M3, M4 and M5, M6 with current sinks M13 and M15, respectively, realize error amplifiers corresponding to  $G^{<3>}$  in Fig. 3. The transistors M9-M12 and M16 work in saturation and implement simple current-mirror circuits. Difference of currents  $i_A$  and i<sub>B</sub> is the output current from the input stage and is equivalent to i<sub>OUT</sub> from Fig. 3. Two capacitors  $C_C$  realize phase compensation at higher frequencies, however, we omit the detailed description of the compensation mechanism here.

Output stage of the OTA is presented in Fig. 7(b) and forms a programmable current mirror array with common mode feedback circuitry (CMFB), which is similar to stage presented in [19]. Note that alternatively, programmable current mirror array can be replaced by programmable current divider [56], [57]. CMFB block works in classical two MOS pair configuration. Programmable current mirror works in cascade configuration with extra MOS devices M4a, M2a, M4b, M2b which improve high frequency response of the mirror [39]. Devices Mo1 and Mo2 are output transistors of the cascaded current mirror, while devices denoted as Ms act as switches that connect biasing voltage  $V_{BIAS1}$  to the upper output transistors. Voltages  $V_{SP\_4} - V_{SP\_0}$  control actual multiplication ratio of the output stage. If voltage  $V_{SP\ X}$  is set to  $V_{DD}$  then  $V_{BLAS1}$  is present on the gate of corresponding device Mo1 and this output current flows to the output of OTA. Otherwise, i.e., if  $V_{SP\ X}$  is set to 0, the corresponding output current is equal zero as well. There are two MOS switches connected to all upper transistors Mo1. Second switch reloads  $C_{GS}$  capacitance to zero and, due to this, control voltages  $V_{SN X}$  should be always inverted versions of corresponding  $V_{SP X}$  voltages. Output stage indexed 0 consists of one set of Mo1 and Mo2 devices. The number of output sets in each subsequent stage is doubled in comparison to the previous stage. There are five output stages indexed from 0 to 4 altogether, and due to this one can obtain 31 different final transconductances of the OTA.

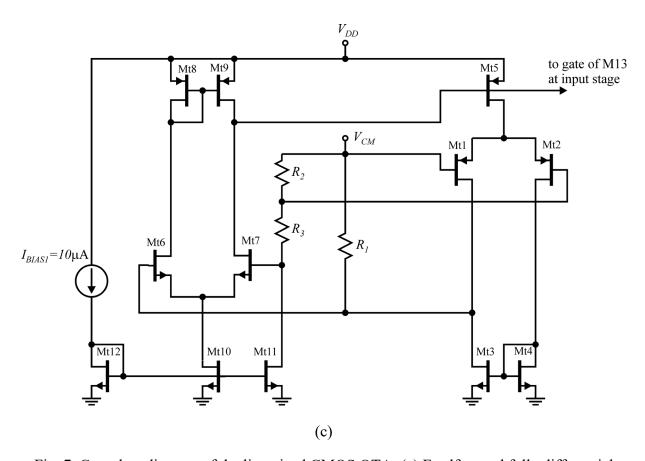

Unfortunately, in order to obtain a linear correspondence between the output current of the input stage presented at Fig. 7(a) and the input differential voltage, precise resistors of values equal to  $1/(2g_{m1,2})$  are required, where  $g_{m1,2}$  is transconductance of the differential pairs M1, M2 and M7, M8. Otherwise, high nonlinearities may occur and linearization schema explained in Section 2 will not work correctly. Therefore, a special circuit performing selfadjustment of the differential MOS pairs is introduced and presented in Fig. 7(c). This gmadjusting block is based on master-slave concept usually applied in automatic circuit parameters control e.g. in intergraded filters design [1-3]. Thus, circuit changes constant polarizing current flowing to the MOS pair Mt1, Mt2 (which should be identical as stabilized MOS pairs M1, M2 and M7, M8). The change of this current causes the corresponding change of transconductance of the MOS pair. Devices Mt6-Mt9 form simple operational amplifier, which works in a closed loop. The result is that the voltage across resistance  $R_1$  and the sum of voltages on  $R_2$  and  $R_3$  are stabilized to the same values. Assuming this equality as well as the MOS pair Mt1-Mt2 working in the linear region, the final transconductance of this differential stage is equal to:

$$g_{m1,2} \approx g_1 = \frac{R_2 + R_3}{R_1 R_2} = \frac{1}{R}$$

(14)

If the same polarizing current is then flown to another identical MOS pair, that pair will have the same transconductance. This is realized by the current mirror with devices Mt5 and M13-M16 from the input stage in Fig. 7(a). Any change in power supply value, temperature, or any change in run to run deviation in the realized resistors can be now easily compensated. This requires extra devices and power but this circuit can be implemented only once for all OTAs in the whole integrated circuit. To obtain the desired value of final transconductance  $g_m=1/R$ , the resistances of  $R_1$ ,  $R_2$  and  $R_3$  should be chosen so that:

$$\frac{R_2 + R_3}{R_1 R_2} = \frac{1}{R} \tag{15}$$

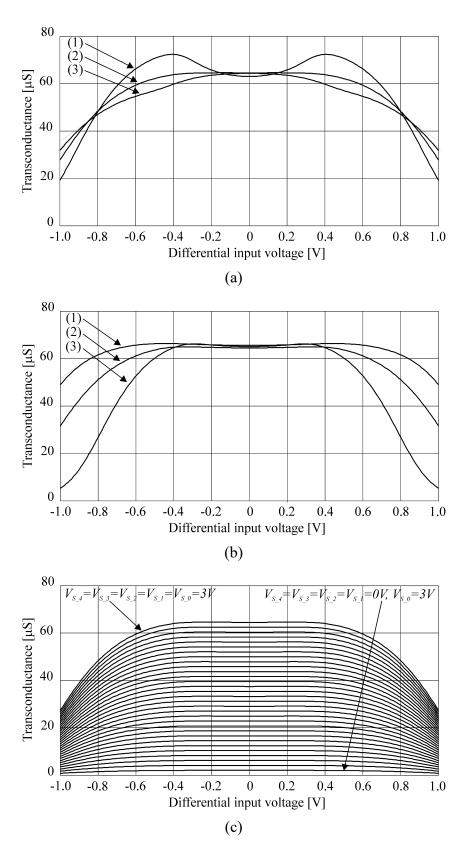

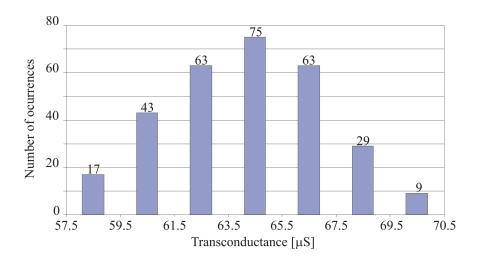

Simulation results of proposed OTA (Fig. 7) are presented in the Table 1 and in Figs. 8 and 9. The results are presented for both versions of OTA, i.e., with and without the  $g_m$ -adjusting circuitry. It is shown that both OTA circuits work well but only the amplifier with the  $g_m$ -adjusting circuitry gives high linearity of the transfer characteristics in case the temperature change occurs. THD of the OTA with  $g_m$ -adjusting for 0.5 V amplitude sine of 10 kHz, and the temperature change from -30 °C to 90 °C is lower than -49.3 dB while for the OTA without  $g_m$ -adjusting THD degrades to -35.8 dB. MOS dimensions (W/L) and resistors of our OTA circuit are given in Table 2.

Table 1. Feedforward linearized OTA parameter comparison ( $V_{DD} = 3V$  and  $I_{BIAS} = 15 \mu A$ )

| Parameter                                                                                                 | OTA without $g_m$ -adjusting | OTA with $g_m$ -adjusting |

|-----------------------------------------------------------------------------------------------------------|------------------------------|---------------------------|

| Maximum transconductance $g_m [\mu S]$                                                                    | 64.5                         | 64.5                      |

| Minimum transconductance [μS]                                                                             | 2.081                        | 2.081                     |

| Power dissipation [mW]                                                                                    | 0.76                         | 0.86                      |

| Open loop voltage gain [dB]                                                                               | 78                           | 77.5                      |

| 3dB bandwidth [kHz]                                                                                       | 58.5                         | 62.8                      |

| Differential input capacitance [fF]                                                                       | 16.4                         | 16.4                      |

| Differential output capacitance [fF]                                                                      | 22.1                         | 22.1                      |

| CMRR for 3% deviation in $V_T$ and 0.5% in K of MOS devices, worst case for 100 Monte Carlo analyzes [dB] | 26.5                         | *                         |

| PSRR for 3% deviation in $V_T$ and 0.5% in K of MOS devices, worst case for 100 Monte Carlo analyzes [dB] | 25.6                         | *                         |

| THD @ input sine with amplitude of 0.5V and at temperatures of -30°C, 30°C and 90°C, respectively [dB]    | -35.8                        | -49.3                     |

|                                                                                                           | -53.3                        | -64.0                     |

|                                                                                                           | -40.2                        | -57.6                     |

<sup>\*</sup> The simulation of CMRR and PSRR parameters with the  $g_m$ -adjustment circuit turned on was not feasible; however, the properly designed adjustment circuit does not change the values of CMRR and PSRR factors significantly when compared to the version of OTA without  $g_m$ -adjustment circuit.

Table 2. MOS dimensions (W/L) and resistors for the OTA circuit of Fig. 7

| Stage                                           | Device Device | Value                    |

|-------------------------------------------------|---------------|--------------------------|

| Stage                                           |               |                          |

| OTA input stage                                 | M1-M8         | 4μm/1μm                  |

|                                                 | M9-M11        | 10μm/1μm                 |

|                                                 | M12, M13, M15 | $30\mu m/1\mu m$         |

|                                                 | M14           | $60\mu m/1\mu m$         |

|                                                 | M16           | 15µm/1µm                 |

|                                                 | Resistors     | $20.4 \mathrm{k}\Omega$  |

|                                                 | $C_C$         | 10fF                     |

| Programmable output stage with the CMFB circuit | M21-M24       | 70μm/2μm                 |

|                                                 | M25, M26      | 4μm/1μm                  |

|                                                 | M27-M30       | $2\mu m/1\mu m$          |

|                                                 | M31, M32      | $10\mu m/1\mu m$         |

|                                                 | Ma1, Mb1      | 6μm/1μm                  |

|                                                 | Ma2, Mb2      | 4μm/1μm                  |

|                                                 | Ma3, Mb3      | 9μm/9μm                  |

|                                                 | Ma4, Mb4      | $12\mu m/0.5\mu m$       |

|                                                 | Mo1           | 4μm/1μm                  |

|                                                 | Mo2           | 1μm/2μm                  |

|                                                 | Ms            | $0.7 \mu m / 0.35 \mu m$ |

| Self-adjusting circuitry for $g_m$              | Mt1-Mt4       | 4μm/1μm                  |

|                                                 | Mt5           | 30μm/1μm                 |

|                                                 | Mt6, Mt7      | 4μm/1μm                  |

|                                                 | Mt8, Mt9      | 15μm/1μm                 |

|                                                 | Mt10-Mt12     | 2μm/2μm                  |

|                                                 | $R_1$         | 59.5kΩ                   |

|                                                 | $R_2$         | $2.88$ k $\Omega$        |

|                                                 | =             |                          |

|                                                 | $R_3$         | 11.52kΩ                  |

#### 4. PROGRAMMABLE OTA-C FILTER DESIGN

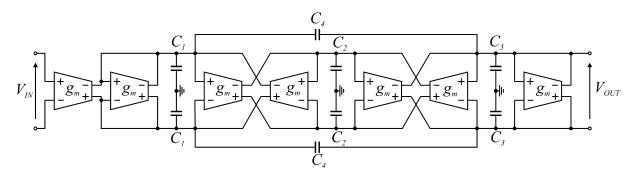

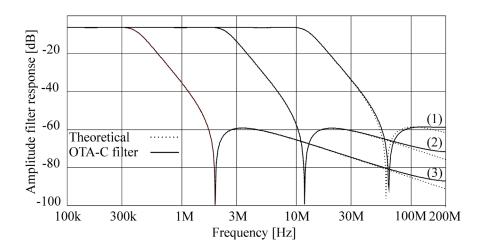

Consider an elliptic filter prototype with rejection in stop band equal to 53.2 dB [54]. Denormalization was carried out for  $g_m = 64.5 \mu S$  and cut-off frequency of 10 MHz. Final filter schematic is presented in Fig. 10. After subtracting OTA's input and output capacitances, filter capacitor values are following:  $C_1 = 2.21 \text{ pF}$ ,  $C_2 = 2.16 \text{ pF}$ ,  $C_3 = 2.25 \text{ pF}$  and  $C_4 = 49.9$  fF. As OTAs, amplifiers with and without  $g_m$ -tuning were used. Simulation results are summarized in the Table 3. Frequency responses of the filter are presented in the Fig. 11. It can be observed that the filter works well and the zero rejection is higher than 66 dB. Frequency response complies with the theory for frequencies up to 100 MHz. Filter with the  $g_m$ -tuning circuitry presents much lower THD distortion if temperature changes occur as shown in Table 3.

Table 3. Performance parameters of the filter in Fig. 10

| Parameter                                                 | Filter built using OTAs without $g_m$ -adjusting | Filter built using OTAs with $g_m$ -adjusting |

|-----------------------------------------------------------|--------------------------------------------------|-----------------------------------------------|

| Maximal cut-off frequency [MHz]                           | 10                                               | 10                                            |

| Minimal cut-off frequency [kHz]                           | 322.6                                            | 322.6                                         |

| Power dissipation [mW]                                    | 5.05                                             | 5.28                                          |

| THD @ sine with 0.5 V of amplitude and frequency          | -39.8                                            | -47.1                                         |

| 10 kHz for temperatures equal to -30 °C, 30 °C and 90 °C, | -53.4                                            | -63.9                                         |

| respectively [dB]                                         | -41.8                                            | -61.8                                         |

#### 5. CONCLUSIONS

A programmable fully differential feedforward CMOS OTA with excellent linearity for highfrequency applications is described and its performance simulated. The circuit is developed using a three-differential-pair transconductor operating in feedforward configuration together with a two-resistor load for introducing the error signal in the active feedforward path. Also a self-adjusting  $g_m$  circuitry operatig in the feedback-loop is developed. The wide range  $g_m$ -programmability is obtained using a programmable current mirror array technique. As an application example, a third-order elliptic OTA-C low-pass filter with cutoff frequency up to 10 MHz is implemented in the AMS 0.35 µm CMOS process.

### REFERENCES

- R. Schaumann, M.S. Ghausi and K.R. Design of Analog Filters, Passive, Active RC, and [1] Switched Capacitor, Prentice-Hall, New York, 1990.

- Y. Tsividis, J.O. Voorman, Integrated continous-time filters: principles, design, and [2] application, IEEE Press, 1993.

- T. Deliyanis, Y. Sun and J.K. Fidler, Continuous-time Active Filter Design, CRS Press, USA, [3] 1999.

- E. Sanchez-Sinencio and J.Silva Martinez, "CMOS transconductance amplifiers, architectures [4] and active filters: a tutorial", IEE Proc. - Circuits Devices Syst., vol.147, no.1, pp. 3-12, 2000.

- S.T. Duie and M. Ismail, High Frequency CMOS Transconductors, in Analogue IC Design: The [5] Current-Mode Approach, Eds. C. Tomazou, F.J. Lidgey, D.G. Haigh, London, Peter-Peregrinius,

- R. Nawrocki, "Electronically controlled ota-c filter with follow-the-leader-feedback structure," [6] *Int. J. Circuit Theory App.*, vol. 16, no. 1, pp. 93-96, 1988.

- C. Acar, F. Anday, H. Kuntman, "On the realization of OTA-C filters," Int. J. Circuit Theory App., vol. 21, no. 4, pp. 331-341, 1993.

- T. Ndjountche, A. Zibi, "Letters to the editor on the design of ota-c structurally allpass filters," [8] Int. J. Circuit Theory App., vol. 23, no. 5, pp. 525-529, 1995.

- Y. Sun, J.K. Fidler, "Resonator-based universal ota-grounded capacitor filters," Int. J. Circuit Theory App., vol. 23, no. 3, pp. 261-265, 1995.

- [10] M. Helfenstein, Q. Huang, G.S. Moschytz, "90 dB, 90 MHz, 30 mW CMOS OTA for a high capacitive load," Int. J. Circuit Theory Appl., vol. 27, no. 5, pp. 473-483, 1999.

- [11] Y. Sun, X. Zhu, J. Moritz, "Explicit design formulas for current-mode leap-frog OTA-C filters and 300 MHz CMOS seventh-order linear phase filter," Int. J. Circuit Theory App., published online 17 Nov. 2008.

- [12] P.Wambacq and W. Sansen, Distortion Analysis of Analog Integrated Circuits, Kluwer Academic Publishers, 1998.

- [13] S. Koziel, A. Ramachandran, S. Szczepanski and E. Sanchez-Sinencio, "A general framework for dynamic range, noise and linearity optimization of continuous-time OTA-C filters," Int. J. Circuit Theory Appl., vol. 35, no. 4, pp. 405-425, July/Aug. 2007.

- [14] S. Koziel, "Analysis of OTA-C filters with weakly nonlinear transconductors," Int. J. Circuit Theory App., vol. 36, no. 7, pp. 789-811, 2008.

- [15] S. Pavan and Y. Tsividis, High Frequency Continuous Time Filters in Digital MOS Processes, Kluwer Academic Publishers, Boston, 2000.

- [16] J.D. Gray, C.M. Twigg, D.N. Abramson, and P. Hasler, "Characteristics and programming of floating-gate pFET switches in a FPAA crossbar network", in Proc. IEEE Int. Symp. Circuits Syst., 2005, vol. 1, pp. 468-471.

- [17] F. Henrici, J. Becker, A. Buhmann, M. Ortmanns, and Y. Manoli, "A Continuous-Time Field Programmable Analog Array Using Parasitic Capacitance G<sub>m</sub>-C Filters", in Proc. IEEE Int. *Symp. Circuits Syst.*, 2007, pp. 2236-2239.

- [18] P. Hasler, and C.M. Twigg, "An OTA-based Large-Scale Field Programmable Analog Array (FPAA) for faster On-Chip Communication and Computation", in Proc. IEEE Int. Symp . Circuits Syst., 2007, vol. 1, pp. 177-180.

- [19] B. Pankiewicz, M. Wojcikowski, S. Szczepanski and Y. Sun, "A Field Programmable Analog Array for CMOS Continuous-Time OTA-C Filter Applications", IEEE Journal of Solid-State Circuits, Vol. 37, No. 2, pp.125-136, Feb. 2002.

- [20] L. Chang, L. Liu, and C. Hu, "A field progrmmable analog array using current mode transconductor-caoacitor (G<sub>m</sub>-C) technique", in Proc. IEEE Asia Pacyfic Conf. Circuits Syst., 2004, vol. 2, pp. 721-724.

- [21] A. St. Leger, C. Nwankpa, "OTA-based transmission line model with variable parameters for analog power flow computation," Int. J. Circuit Theory App., published online 10 Nov. 2008.

- [22] K. Bult and H. Wallinga, "A class of analog CMOS circuits based on the square-law characteristic of an MOS transistor in saturation" IEEE J. Solid State Circuits, 22(3), pp. 357-365, 1987.

- [23] H.Khorramabadi and P.R. Gray, "High frequency CMOS continuous-time filters", IEEE J. Solid State Circuits, SC-19, 939-948, 1984.

- [24] S. Szczepanski, J. Jakusz and R. Schaumann, "A linear fully balanced CMOS OTA for VHF filtering applications", IEEE Trans. Circuits Syst.-II 44, pp. 174-187, 1997.

- [25] S. Koziel and S. Szczepanski, "Design of highly linear tunable CMOS OTA for cotinuous-time filters", IEEE Trans. Circuits Syst.-II 49(2), pp. 110-122, 2002.

- [26] Y. Tsividis, "Integrated continuous-time filter design an overview", IEEE J. Solid State Circuits, 29, pp. 166-176, 1994.

- [27] A.P. Nedungadi and T.R. Viswanathan, "Design of linear CMOS transconductance elements", *IEEE Trans. Circuits Syst.* CAS 31, pp. 831-834, 1984.

- [28] A.P. Nedungadi and R.L. Geiger, "High frequency voltage controlled continuous time low-pass filter using linearized CMOS integrators", Electron. Lett., 22, pp. 729-731, 1986.

- [29] M.I. Ali, M. Howe, E. Sanchez-Sinencio and J. Ramrez-Angulo, "A BiCMOS low distortion tunable OTA for continuous-time filters", IEEE Trans. Circuits Syst.-40, pp.43-49, 1993.

- [30] F. Krummenacher and N. Joehl, "A 4-MHz CMOS continous-time filter with on-chip automatic tuning", IEEE J. Solid State Circuits, 23, pp. 750-758, 1988.

- [31] J.M. Khoury, "Desgn of a 15-MHz CMOS continuous-time filter with on chip tuning", *IEEE J.* Solid State Circuits, 26, pp. 1988-1997, 1991.

- [32] Z. Wang and W. Guggenbuhl. "A voltage-controllable linear MOS transconductor using bias offset technique", IEEE J. Solid State Circuits, 25, pp. 315-317, 1990.

- [33] R. Alini, A. Baschirotto and R. Castello, "8-32 MHz tunable BiCMOS continuous-time filter for high-frequency applications", IEEE J. Solid State Circuits, 27, pp. 1905-1915, 1992.

- [34] P.Wu, R.Schaumann and S.Szczepanski, "A CMOS OTA with improved linearity based on current addition", in Proc. IEEE Int. Symp. Circuits and Syst., pp. 2296-2299, 1990.

- [35] J. Glinianowicz, J. Jakusz, S.Szczepanski and Y. Sun, "High-frequency two-input CMOS OTA for continuous-time filter applications", IEE Proc.-Circuit Devices Syst., 147(1), pp. 13-18, 2000.

- [36] P. Monsuro, S. Pennisi, G.Scotti and A. Trifeletti, "Linearization Technique for Source-Degenerated CMOS Differential Transconductors", IEEE Trans. Circuits Syst.-II 54(10), pp. 848-852, 2007.

- [37] T.S. Lande and Y. Berg, "Ultra low voltage transconductance amplifier", in *Proc. IEEE Int.* Conf. on Electronics, Circuits and Systems, pp. 333-336, 1998.

- [38] M. Teresa Sanz, S. Celma, B. Calvo, "Using MOS current dividers for linearization of programmable gain amplifiers" Int. J. Circuit Theory App., vol. 36, no. 4, pp. 397-408, 2008.

- [39] G. Di Catalo, G. Palumbo, and S. Stivala, "New CMOS current mirrors with improved highfrequency response", Int. J. Circuit Theory and Applications, Vol. 21, pp. 443-450, 1993.

- [40] R.G. Meyer, R. Eschenbach and W.Edgerley, "A wide-band feedforward amplifier", IEEE J. Solid State Circuits, SC-9(6), pp. 422-428, 1974.

- [41] S. Szczepanski and Z.P. Tomaszewski, "Linearization technique using the mixed feedforwardfeedback concept" in Proc. European Conference on Circuit Theory and Design (ECCTD), 1, pp.214-219, 1980.

- [42] S. Narahashi and T.Nojima, "Extremely low-distortion multi-carrier amplifier self-adjusting feedforward amplifier", in Proc. IEEE Int. Communication Conf., pp. 11485-1490, 1991.

- [43] J.K. Cavers, "Adaptation behavior of feedforward amplifier linearizer", IEEE Trans. Vehicular Tech. 44(1), pp.31-40, 1995.

- [44] E.E. Eid, F.M. Ghannouchi and F. Beauregard, "Optimal feedforward linearization system design", Microwave Journal 38(11), pp.78-86, 1995.

- [45] P.B. Kenington and D.W. Bennet, "Linear distortion correction using a feedforward system", *IEEE Trans. Vehicular Tech.* 45(1) pp. 74-81, 1996.

- [46] Q. Cheng, C.Yiyuan and Z. Xiaowei, "A 1.9 GHz adaptive feedforward power amplifier", Microwave Journal, 41(11), pp. 86-96, 1998.

- [47] A. Katz, "Linearization: reducing distortion in power applifiers", IEEE Microwave Magazin, 2-4, pp. 37-49, 2001.

- [48] S. Szczepanski, S. Koziel and E. Sanchez-Sinencio, "Linearized CMOS OTA using active-error feedforward technique", in Proc. IEEE Int. Symp. Circuits Syst., vol.1, 2004, pp. 549-552.

- [49] A.B. Grebene, Bipolar and MOS Analog Integrated Circuit Design, John Wiley & Sons, Inc., New York, 1984.

- [50] W. Sansen and Z.Y. Chang, "Feedforward compensation techniques for high-frequency CMOS amplifier", IEEE J. Solid State Circuits, 25(6), 1990.

- [51] S. Setty, S. C. Toumazou, "Feedforward compensation technique in the design of low voltage opamps and OTAs", in Proc. IEEE Int. Symp. Circuits Syst. I, 1998, pp. 464-467.

- [52] B. H. Thandri and J.Silva-Martinez, "A robust feedforward compensation scheme for multistage operational transconductance amplifiers with no Miller capacitors", IEEE J. Solid State Circuits, 38(2), pp. 237-243, 2003.

- [53] S. Szczepanski, S. Koziel, "Phase compensation scheme for feedforward linearized CMOS operational transconductance amplifier", Bulletin of the Polish Academy of Sciences, Technical Sciences, vol.52, no.2, pp. 141-148, 2004.

- [54] A. B. Williams, F. J. Taylor, "Electronic Filter Design Handbook, LC, Active and Digital Filters", Mc Graw-Hill Publishig Company, 1988.

- [55] C. A. Leme, J. Silva, P. Rodrigo, J. Franca, "A low-power CMOS nine-channel 40-MHz binary detection system with self-calibrated 500-µV offset", IEEE J. Solid State Circuits, 33(4), pp. 565-572, 1998.

- [56] K. Bult, G. Geelen, "An inherently linear and compact MOST-only current division technique", IEEE J. Solid State Circuits, 27(12), pp. 1730-1735, 1992.

- [57] Y.Deng, S. Chakrabartty, G. Cauwenberghs, "Three-decade programmable fully differential linear OTA", in Proc. IEEE Int. Symp. Circuits Syst. I, 2004, pp. 697-700.

Fig. 1. Nonlinear model of transconductance element: (a) Symbolic representation. (b) Nonlinear incremental equivalent circuit.

Fig. 2. Simple CMOS differential pair transconductor.

Fig. 3. Three-block feedforward transconductance amplifier [49], [52].

Fig. 4. Theoretical THD characteristics for (1) simple differential-pair transconductor, and (2) linearized transconductor.

Fig. 5. Theoretical transfer characteristics for (1) simple differential-pair transconductor, and (2) and linearized transconductor (2).

Fig. 6. Theoretical transconductance characteristics for (1) simple differential-pair transconductor, and (2) linearized transconductor.

Fig. 7. Complete diagram of the linearized CMOS OTA: (a) Feedforward fully differential input stage. (b) Programmable output stage with the CMFB circuit, (c) Self-adjusting  $g_m$  circuitry.

Fig. 8. Simulated transconductance of OTA from Fig. 7: (a) without  $g_m$ -adjusting, and (b) with  $g_m$ - adjusting for three operating temperatures: (1) -30 °C, (2) +30 °C, and (3) +90 °C, and (c) change of transconductance  $g_m$  parameters by digital programming word at lines  $[V_{S\_4}: V_{S\_0}]$ .

Fig. 9. Monte-Calro simulation results for transconductance of OTA from Fig. 7 without  $g_m$ -adjusting circuitry for 3% deviations in threshold voltage and 0.5% in transconductance parameter of MOS devices. Results for 300 random simulations.

Fig. 10. Third-order low-pass OTA-C elliptic filter.

Fig. 11. Simulated response of OTA-C filter from Fig. 10 for OTA transconductance  $g_m = 64.5 \,\mu\text{S}$  (1),  $g_m = 12.48 \,\mu\text{S}$  (2) and for  $g_m = 2.081 \,\mu\text{S}$  (3). Change of transconductance was carried out through voltages applied to  $V_{SP\_4}$  -  $V_{SP\_0}$  and  $V_{SN\_4}$  -  $V_{SN\_0}$ .