Postprint of: Kłosowski M., Jakusz J., Jendernalik W., Blakiewicz G., Szczepański S., Kozieł S., A High-Efficient Measurement System With Optimization Feature for Prototype CMOS Image Sensors, IEEE Transactions on Instrumentation and Measurement, Vol. 67, Iss. 10 (2018), pp. 2363-2372, DOI: 10.1109/TIM.2018.2814118

© 2018 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

# A High-Efficient Measurement System With Optimization Feature for Prototype CMOS Image Sensors

M. Kłosowski, J. Jakusz, W. Jendernalik, G. Blakiewicz, S. Szczepański, and S. Kozieł, Senior Member, IEEE

Abstract-In this paper, a gray-scale CMOS image sensor (CIS) characterization system with an optimization feature has been proposed. By using a very fast and precise control of light intensity, based on the pulsewidth-modulation method, it is avoided to measure the illuminance every time. These features accelerate the multicriteria CIS optimization requiring many thousands of measurements. The system throughput is 2.5 Gb/s, which allows for capturing images from large arrays of the size 3000 x 3000 pixels at the rate of 25 frames/s, or small arrays (128  $\times$  128) at the rate of 15000 frames/s. The efficient transfer of measurement data to the external software allows immediate presentation of optimization results in 3-D plots. The system automatically measures nonuniformity, spatial noise, temporal noise, signal-to-noise ratio, dynamic range, nonlinearity and image lag. A flat diffuser has been proposed as a cheaper alternative to an integrating sphere. This optical front-end is particularly useful for testing prototype CISs and vision-chips implemented in standard CMOS technologies as low- or mediumdynamic-range imagers.

Index Terms—CMOS image sensor (CIS), CMOS imager, imager characterization, imager optimization, imaging array.

# I. Introduction

PRINCIPAL performance of CMOS imagers (CIS) include nonuniformity, signal-to-noise ratio (SNR), dynamic range (DR), nonlinearity, image lag, and speed of image acquisition [1]. The reliable characterization of CIS requires a step change in light intensity, where the number of steps can be up to several thousand. The characterization of a prototype imager can take place simultaneously with its optimization, for example on finding the optimal levels of signals controlling a transfer gate (TG), reset gate, etc. Optimization requires repeating a series of measurements for many thousands of light intensity levels. Classical measurements consisting of a step change in light intensity and simultaneous measurement of illuminance (or irradiance) on the CIS surface are too slow in

This work was supported in part by the National Science Centre of Poland under Grant 2011/03/B/ST7/03547 and Grant 2016/23/B/ST7/03733.

The authors are with the Faculty of Electronics Telecommunications and Informatics, Gdańsk University of Technology, 80-233 Gdańsk, Poland, and also with the School of Science and Engineering, Reykjavik University, 101 Reykjavik, Iceland (e-mail: waljende@pg.gda.pl; koziel@ru.is).

the case of repeating many measurement series. The slowdown is mainly due to the delay introduced by the light meter and light intensity adjustment procedures. In addition, for some measurements, e.g., differential nonlinearity (DNL) using a histogram method, the light intensity should be changed in very small and equal steps, which makes measuring difficult and longer.

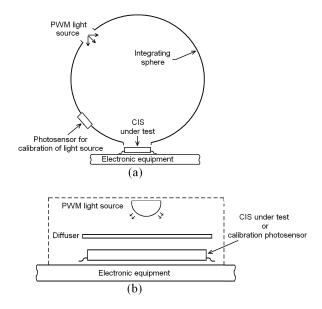

Alternatively, the measurements can be done using a pulsed light source with constant intensity of pulses whose duty factor is regulated. With this approach a quick and precise change of the illuminance is obtained without the need to calibrate the light source for each level of illuminance. The pulsed light source can be used in measuring systems with an integrating sphere or in systems with a flat diffuser, as shown in Fig. 1(a) and (b). An integrating sphere is necessary for the characterization of imagers with high DR (>10 bit), e.g., it has been used in [2] to test CIS of dynamic of over 15 bits (90 dB) and low nonlinearity below -70 dB. In CISs with lower DR, the simpler solution with a flat diffuser may also be used [Fig. 1(b)]. The system of Fig. 1(b) is dedicated for prototype gray-scale imagers or vision-chips implemented in cheap standard CMOS technologies and featuring low and medium DR 6-10 bits [3]-[13].

The research on CIS is often hindered by inaccessibility of appropriate and sufficiently accurate measurement platforms. Prototype image sensors are often characterized by nonstandard properties and their designers must develop tailored measurement systems. On the other hand, development of suitable measurement system may be more time consuming than design of the CIS itself. Literature (see [10], [11], [13]–[15]) provides brief descriptions of the measurement platforms; however, due to the lack of details, they are difficult to be replicated.

This paper provides a detailed description of a complete measurement system of the architecture of Fig. 1(b), which consists of easily accessible components and can be easily replicated. The proposed system is computationally efficient, and permits the characterization of gray-scale imagers with a DR of up to 10 bits. It measures parameters such as: dark signal nonuniformity (DSNU), photoresponse nonuniformity (PRNU), temporal noise, fixed pattern noise (FPN), integral nonlinearity (INL), DNL, SNR, DR, as well as image lag. The system employs the mechanisms facilitating imager testing such as possibility of online picture preview, hardware PRNU compensation, as well as synchronization of the light

Fig. 1. Measurement systems with PWM light source. (a) Version based on an integrating sphere. (b) Cheaper version based on a diffuser.

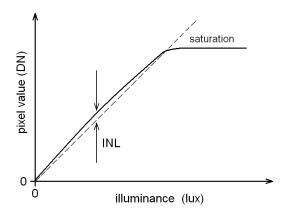

Fig. 2. Typical photoconversion characteristic (solid line) of linear CISs.

source with the imager shutter. An additional feature is a possibility of generating 3-D plots which can be used to determine optimum operating conditions of the imager under test and interpretation of the phenomena that influence the measurement results. There are two types of photosensors that CMOS image sensor (CIS) can be handled with: an integration mode photodiode and an MOS photogate (PG). Owing to a dedicated measurement algorithm, the system permits automated determination of the optimum photosensor controlling signals (i.e., the reset, PG, and TG signals).

# II. GENERAL REQUIREMENTS FOR MEASUREMENT SYSTEM

One of important imager measurements is determination of the photoconversion characteristic, i.e., dependence between illuminance and the pixel value. Fig. 2 shows a typical response of a linear image sensor. Due to technological/manufacturing mismatch and temporal noise, pixel characteristics differ from each other. Consequently, photoconversion characteristic of the imager is an average over all pixels in the array. The spread of pixel responses due to mismatch and temporal noise manifests itself as the spatial noise. The part of the spatial noise caused by the temporal noise of individual pixels is referred to as random spatial noise. The part of the spatial noise related to the mismatch (and to 1/fnoise at very low frequencies) is referred to as FPN. The pixel response spread caused by the mismatch determines nonuniformity of the image sensor. It is characterized by two parameters, DSNU and PRNU. Random noise and FPN are the main factors that determine SNR and DR of the imager. In practice, the characterization of the image sensor is related to carrying out multiple operations such as the measurement of responses of each pixel under various illumination intensities, the separation of the random noise from the fixed pattern, making histograms, and the calculation of standard deviations. The entire process is related to acquisition and processing of large amounts of data so that the measurement system should be able to process visual data in real time at sufficiently high speed. Furthermore, the measurement system should be able to provide appropriate illumination and imager control signals. These requirements will be discussed in detail in the subsequent sections.

#### A. Uniformity of Illumination

Uniform illumination is necessary to determine nonuniformity and SNR of the image sensor. Illumination nonuniformity should be lower than the assumed nonuniformity of the pixel array. In practice, it can be assumed that illumination nonuniformity should be lower than 0.5 LSB. For example, for a 9-bit CIS, it should be lower than 0.1%. Typically, an opal diffusing glass or white diffusing glass should be used for this application. (The transmitted light will be near-Lambertian.) With such diffuser and a multilight-emitting diode (LED) light source, acceptable illumination nonuniformity can be easily achieved.

# B. Illuminance Range

A required illuminance range is from 0 lux (darkness) to a certain maximum level which may be quite different for CIS implemented using various techniques and realized in different technologies. The maximum useful light intensity may be limited by the "overexposure" phenomenon which is basically a lateral light propagation in SiO<sub>2</sub> in the integrated circuit and interfering operation of the covered electronic circuitry. For example, for an imager of [6] this value is about 500 lux.

# C. Number of Illuminance Levels

Controlling illumination intensity should be realized with sufficiently small steps and nonlinearity, which is necessary to determine a photoconversion characteristic of the imager. The actual characteristic is most often slightly bended up, as shown in Fig. 2. It is difficult to decide beforehand what should be the number of measurement points in order to correctly determine INL and DNL characteristics. It can be anything from a few to a few thousand points. For example, in order to determine INL of the sensor of [6] only 30 measurement points were

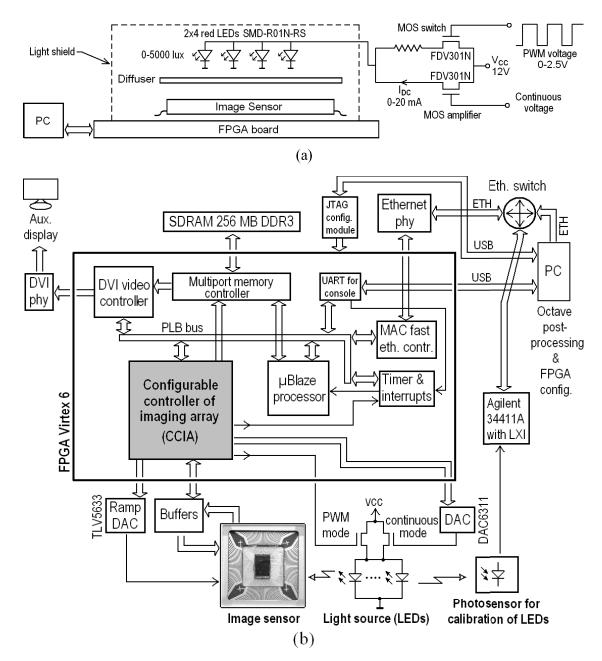

Fig. 3. Developed measurement system. (a) Simplified diagram. (b) Detailed diagram.

necessary (INL < 0.5%). At the same time, the measurement of DNL of the same sensor using a histogram method required 10 000 illuminance levels (DNL < 0.5 LSB).

# D. Spectrum of Light

The most appropriate testing light is the white one, however, the realization of the light source with stable spectrum and wide range of illumination intensity is not easy. Monochrome light source is simpler and cheaper. A good choice is a red light, which is because silicon-based CISs are the most sensitive to it. Measurements performed at the highest sensitivity allow us to reduce—while determining photoconversion characteristic—contribution of unwelcome phenomena such as reflection and interferences at the top glass layer of the integrated circuit.

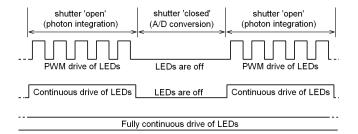

## E. Synchronization of Illumination With Shutter

Synchronization of illumination with an electronic shutter means that the light is turned ON only when the shutter is open, i.e., when the pixel photosensors are integrating photons, whereas the remaining electronic circuits remain inactive. Synchronization is necessary to measure the image lag. Without it, the measured image lag will be overestimated. Implementation of synchronization will be discussed in detail in Section III-A.

# F. Electronic Equipment: Control Signals and Data Throughput

The measurement system should produce typical digital and analog signals controlling the operation of the CIS under test. For example, these can be signals controlling the TG and the

Fig. 4. PWM (upper waveform), continuous (middle waveform), and fully continuous (lower waveform) modes of LEDs driving. In the PWM and continuous modes, LEDs are synchronized with an electronic shutter of an image sensor.

reset transistor (RST), which are present in majority of the typical CMOS pixels. Other typical controlling signals present in imagers are controlling signals for pixel array addressing and reading of visual data, signals controlling analog-to-digital converters (ADCs), reference ramp signal, etc.

Requirement concerning the throughput of visual data depend on the pixel array size, the number of ADC bits built-in the sensor, and the number of frames per second. For example, in order to measure  $512 \times 512$  array of 10-bit pixels at the speed of 1000 frames/s, the required throughput is at least  $(512)^2 \times 10 \times 1000 = 2.6$  Gb/s. It is comparable with the throughput of the HDD SATA2 bus; therefore, implementation of the measurement chain is far from trivial.

#### III. ARCHITECTURE OF THE MEASUREMENT SYSTEM

The measurement system that satisfies the requirements discussed in Section II has been shown in Fig. 3. Fig. 3(a) and (b) shows a simplified and detailed diagram of the system, respectively. The system components are discussed below.

#### A. Light Source: Implementation and Calibration

The light source is realized using monochrome LEDs SMD-R01N-RS by Sloan, of the wavelength 610–635 nm (red light). The LEDs are positioned about 40 mm from the CIS surface and can produce illuminance of up to 5000 lux. Illumination intensity can be controlled in two regimes: pulsewidth-modulation (PWM) or continuous. The diode control and synchronization of illumination with the shutter has been explained in Fig. 4.

In PWM regime, the diodes generate a sequence of identical light pulses, i.e., the pulses have the same intensity and duration, they are uniformly allocated in time, and their number during the shutter opening is 36 for 50 frames/s and 1 for 500 frames/s. The change of illumination intensity is realized by changing the duty factor of the pulses. The maximum accuracy of changing the pulselength is 10 ns, which allows for adjusting the illuminance in the range 0–5000 lux with the minimum step of  $5000/2^{16} \approx 0.08$  lux. Such a small step may be useful for DNL measurement using the histogram method [6]. Assuming constant temperature, intensity of the light emitted by the LEDs is stable over time. Maintaining constant temperature is facilitated by a dedicated algorithm that determines a sequence of illumination intensity changes

during measurements (such that the average LED power remains constant). Illuminance is given as

$$E_{\nu}(n) = \frac{E_{\nu \max}}{N} \cdot \begin{cases} 1 + \frac{n-1}{2} & \text{for odd } n \\ N - \frac{n-2}{2} & \text{for even } n \end{cases}$$

(1)

where  $n \in [1, N]$  is the measurement index,  $E_{\nu}$  is illuminance set for the measurement n, and N is an (even) total number of measurements, whereas  $E_{\nu \text{max}}$  is the maximum illuminance.

In the proposed measurement system of Fig. 3, a device measuring the CIS illuminance is not needed. Instead, one-time calibration of the LED illumination is sufficient. For the purpose of calibration, an additional measurement chain has been developed that contains a photosensor (replacing the CIS at the calibration stage) and the photocurrent meter. The Agilent 34411A multimeter with Ethernet interface has been used, which permits automation of the calibration procedure. Nonlinearity of the light intensity adjustment at the level of 0.02% (within the range 0–400 lux) is obtained by calibrating the LEDs just for one light intensity level. In practice, the calibration should be performed for the maximum illumination level pertinent to a CIS under test.

The pulse-based (PWM) illumination intensity adjustment is very precise but the speed of the image frame capturing is limited to 500 frames/s. (Maximum time step of illuminance change is 0.5 ms.) For higher speeds, a continuous light controlling mode has been implemented (time step of illuminance change is 1  $\mu$ s). In this mode, the LEDs are supplied by a dc current  $I_{DC}$ , the value (0-20 mA) of which is proportional to the signal from a 10-bit DAC (DAC6311 by Texas Instruments, Chennai, India). Because of nonlinearity of the current-to-light characteristic of the LEDs and voltage-to-current characteristic of the MOS amplifier (FDV301N by Fairchild, Sunnyvale, CA, USA), the illumination system requires calibration for each illumination level. However, despite calibration at all levels, the resolution, linearity and time stability of the light source in this mode is worse than for the PWM mode. In the developed system, the continuous mode allows illumination adjustment in 100 steps with 0.2% nonlinearity.

# B. Electronic Equipment: System Control and Data Acquisition

The measurement system as well as data acquisition and processing are controlled by a field-programmable gate array (FPGA) circuit and a PC computer.

The main unit for hardware realization of CIS control signals and measurements have been implemented using Xilinx Virtex6 FPGA. It is marked as configurable controller of imaging array (CCIA) [see Fig. 3(b)]. This module is an innovative solution that permits efficient, fast, and automated realization of various types of measurements of image arrays. The unit generates the signals controlling LEDs, pixel array, data reading circuits of the image sensor, as well as the external DAC (TLV5633 by Texas Instruments, Chennai, India) that produces an analog ramp signal. Furthermore, the CCIA unit is responsible for visual data acquisition and synchronization of the operation of the remaining units implemented in FPGA.

Fig. 5. Photograph of the developed measurement system without the light source.

The remaining units include: MicroBlaze processor working under Linux operating system, multiport memory controller that allows the peripherals to access synchronous dynamic random-access memory (SDRAM) in direct memory access mode, medium access control fast Ethernet controller for communication with an external measurement system (e.g., for light source calibration) and the PC machine, the universal asynchronous receiver-transmitter unit that permits realization of the console interface for Linux system in the MicroBlaze processor, and interrupt and timer unit (Timer and Interrupts).

The measurement data are processed and visualized in an external PC machine equipped with a mathematical software Octave. The PC is also used to perform FPGA board configuration and to modify the measurement control software, which is implemented there. The file system of the PC is made accessible for FPGA through Network File System (NFS) (using the Ethernet interface), which facilitates access to the measurement data generated on FPGA.

The measurement system also contains Digital Visual Interface video controller, which is used to visualize the operation of the imager under test. The frames from the tested imager can be observed in the real time using an external monitor.

A photograph of the system has been shown in Fig. 5.

# IV. MEASUREMENT SYSTEM FUNCTIONS

The main control application (executed in MicroBlaze processor on the FPGA board) has been written in C. It realizes the tests and measurements described in Sections IV-A–IV-H.

# A. Calibration and Test of Light Source

The calibration and test function is executed once for a particular type of LED before starting measurements of the image sensor. During the measurements, the function is also used for manual adjustment of the light intensity. The intensity can be controlled in the PWM or continuous mode.

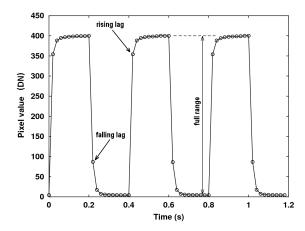

Fig. 6. Example of the time response of an image sensor. Acquisition speed is 50 frames/s. Light pulse frequency is 2.5 Hz.

#### B. Measurement of Nonuniformity and Temporal Noise

This function initiates measurement of temporal noise and nonuniformity of the pixel array in darkness and for one predefined illumination intensity. (The light is turned ON using calibration and test of light source function.) The measurement system acquires up to 1000 subsequent image frames to SDRAM DDR3 system memory. A large number of frames are required in order to separate the static noise (FPN) from the temporal noise. It is possible to omit a selected number of initial frames in order to eliminate the effect of the transient states and the time necessary to establish the operating point of the pixel on the measurement results. The acquired frames are exported to a file and, using NFS, these frames are becoming accessible at an external PC. Further processing of the frames is realized by the Octave software which plots the histogram of the pixel values, calculates DSNU and PRNU, plots the temporal noise spectrum and calculates its RMS value. It is possible to limit the ranges of columns and rows of the pixel array for which the computations are executed (e.g., in order to eliminate the effect of defective pixels on the measurement results). Finally, handling of negative pixel values is also implemented. These may occur when realizing correlated double sampling with no illumination.

The measurement time of nonuniformity and temporal noise is about 30 s for 1000 frames at 50 frames/s.

# C. Automatic Measurement of Nonuniformity, Random Noise, SNR, DR, and Nonlinearity

Upon initializing this function, illumination is changed automatically within the prescribed range and the number of steps. For each illumination level, hardware-based acquisition of a required number (maximum of 1000) of image frames into the system memory is executed. The number of illumination intensity levels can be up to 10000 (see Section II-C), so that the total number of acquired frames may be as high as ten million. In order to increase the processing efficiency, the frames are not being sent to the PC right away (as it was the case for the previously discussed function) but they are preprocessed in FPGA (using the MicroBlaze processor). The processor calculates three parameters: the average pixel value, the standard deviation of the pixel value related to the static

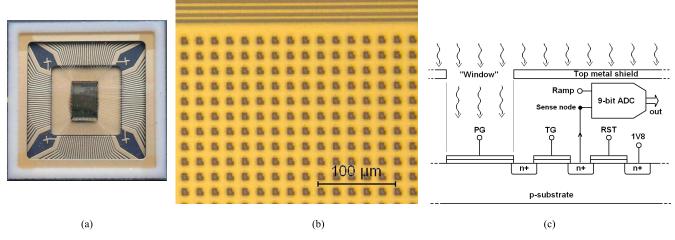

Fig. 7. Prototype CIS fabricated in 0.18-µm technology. (a) Chip. (b) Microphotograph of the portion of a pixel array. (c) Simplified diagram of a pixel.

noise (mismatch), and standard deviation due to the temporal noise. These parameters are determined for each illuminance level and written to a file, which is subsequently processed by Octave. Several scripts have been developed for plotting photoconversion light-to-DN characteristics and for plotting INL, DNL, FPN, temporal noise, and SNR as a function of the illuminance; DR is calculated as well. It is also possible to carry out the aforementioned measurements as a function of other variables than the illuminance, e.g., the number of frames per second.

The measurement time is from one to a few hours depending on the number of steps and the number of acquired frames.

# D. Measurement of Image Lag

During measurement of the "image lag" (remainder of the previous-frame image), the light is turned ON and OFF (or switched between two chosen intensity levels) for the acquisition time of a prescribed number of frames. Furthermore, the light is turned ON/OFF simultaneously with the beginning of photon integration in the pixels. The adjustment of illumination intensity during this stage is either in PWM or a continuous mode according to Fig. 4. A sequence of up to 1000 frames is stored in SDRAM DDR3 memory and, subsequently, sent to the PC and processed by Octave. It is possible to plot the time response of the imager, from which one can extract the "image lag" parameter (in percent). For the sake of example, Fig. 6 shows a time response of the imager of [6]. It is the actual plot obtained from the proposed measurement system. The imager has been excited by the light turned ON and OFF with the frequency of 2.5 Hz. Circles denotes the time points corresponding to frame capture (acquisition speed 50 frames/s). The lag can be observed both during the transition from illumination to darkness (21% of the full range) and in the opposite direction (11% of the full range).

## E. Generation of PRNU Compensation File

Certain image sensors have built-in memory of pixel sensitivity correction coefficients (which is for PRNU correction). In the presented measurement system it is possible to automatically generate a file containing these correction coefficients.

To this end, the average values of all pixels are measured at a prescribed illumination level. This data can contain errors due to, e.g., defective pixels, so that further processing and interpretation of the data are realized by Octave. The file with correction coefficients can be used for initialization of the correction memory of the imager and to verify the efficiency of PRNU compensation. If the image sensor is not equipped with the correction mechanism, the correction can be (hardware-based) performed in the measurement system. In order to enable this capability, a hardware multiplier has been implemented in CCIA which corrects the gain of each pixel upon reading the pixel value.

## F. Test of Array Reset

The test carries out the imaging array reset sequence. The sequence generator has been implemented in Very high speed integrated circuit Hardware Description Language which makes it is easy to work with various CISs. Upon finishing the reset sequence, a number and coordinates of defective pixels (those that were not correctly reset) are displayed.

# G. Test of Array Readout

This test realizes multiple readouts of the entire image array, which allows for readout circuit tests, identifying allocation of defective pixels, and determination of the maximum readout clock frequency.

#### H. Picture Preview and Movie Capture

The function picture preview allows for previewing the image from the CIS under test (at the speed of up to 50 frames/s) using an auxiliary display. The preview facilitates, e.g., adjustment of the lens parameters (focus, zoom, aperture).

The function movie capture allows for capturing up to 1000 image frames at the speed from 50 to 5000 frames/s and writing them in a popular uncompressed format YUV4MPEG2 (extension .y4m).

The proposed measurement system has also been equipped with other functions that will not be discussed in detail. These include measurement of sense-node voltage (recalculating digital value of the pixel into the sense-node voltage of the pixel),

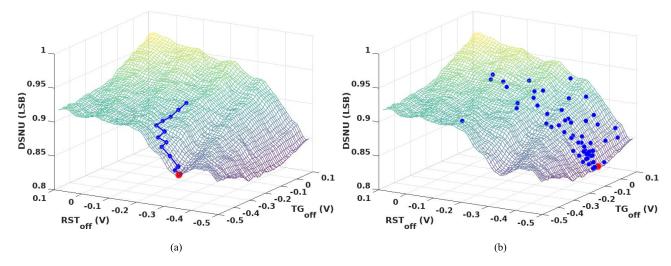

Fig. 8. DSNU of the CIS as a function of the voltages  $TG_{OFF}$  and  $RST_{OFF}$ . (a) Process of a *local search* optimization algorithm (blue line) and the final result of an optimization (red dot). (b) Process of a random search optimization algorithm (blue dots) and the final optimization result (red dot).

test of ADCs (verifying correctness of the ADC converters in the image sensor), and quick test of array, which is automated sequential execution of the three tests: test of array reset, test of array readout, and test of ADCs.

#### V. RESULTS OF SAMPLE MEASUREMENTS

In order to demonstrate the efficiency and capabilities to the developed measurement platform, this section presents the measurement results of an example CIS implemented in a standard 0.18- $\mu$ m CMOS technology [Fig. 7(a)] [6]. As a part of postproduction tests, a number of measurements have been performed, one of which (concerning the image lag) has been already shown in Section IV-D (Fig. 6).

#### A. Tested Imager

The tested prototype CIS contains pixels with MOS PG photosensors as well as 9-bit ADC [Fig. 7(c)]. The pixel array is covered with the top metal layer, which protects ADCs from light. The microphotograph [Fig. 7(b)] reveals windows, i.e., places which are not covered by the metal, allowing the light to reach the photosensors. The size of the imaging array is  $128 \times 128$  pixels with the pixel pitch of  $21~\mu\text{m}$ . The prototype circuit is characterized by significantly higher than typical (25–100 frames/s) image acquisition speed, which is over 3000 frames/s.

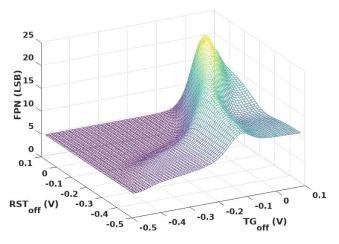

In order to demonstrate nonstandard capabilities to the measurement system, the process of optimizing the control of the MOS-type PG photosensors will be presented. These photosensors utilize a charge transfer mechanism similar to that used in CCD devices [16]. Nonuniformity and nonlinearity of the image sensor is mostly dependent on the parameters of the signals controlling the transistor gates: photosensitive (PG), transferring (TG), and resetting (RST). In this paper, we only present the most important dependencies, in particular, how DSNU, light-FPN (containing DSNU and PRNU), and INL are affected by the voltage levels switching off the transfer transistors (TG<sub>OFF</sub>) and the RSTs (RST<sub>OFF</sub>). Measurement of

DSNU, PRNU, and INL requires acquisition and averaging of a few dozen to a few hundred of frames (necessary to remove random noise). Furthermore, in case of INL, it is necessary to repeat the measurements for a few dozen of illumination intensities. Subsequently, the measurements have to be repeated for all combinations of voltages  $TG_{OFF}$  and  $RST_{OFF}$ . The obtained results have been shown in Figs. 8-13.

# B. Optimum of DSNU

Fig. 8 shows dependence between DSNU and voltages  $TG_{OFF}$  and  $RST_{OFF}$ . The measurement has been performed for all possible combinations of  $TG_{OFF}$  and  $RST_{OFF}$  with 10-mV step. The plot allows identifying the voltage levels that ensure minimum DSNU. Such a brute force (and exhaustive) approach is accurate but time consuming. In the considered case, measurements took about 200 min.

In order to reduce the overhead related to identifying the optimum values of the voltages (for which DSNU reaches its minimum), the measurement system has been equipped with optimization algorithms. The operation of the hill-climbing procedure [17] (which is a local search routine) has been illustrated in Fig. 8(a). The blue line shows the path followed by the optimizer. (The red dot marks the local minimum found.) Another algorithm implemented in the system is a Luus–Jaakola [18] routine which is a sequential quasi-global stochastic procedure that partially alleviates difficulties related to the presence of multiple local optima. Operation of the algorithm has been shown in Fig. 8(b). Clearly, the stochastic algorithm converges slower than the hill-climbing method; nevertheless, the optimization time is reduced to only 4 min.

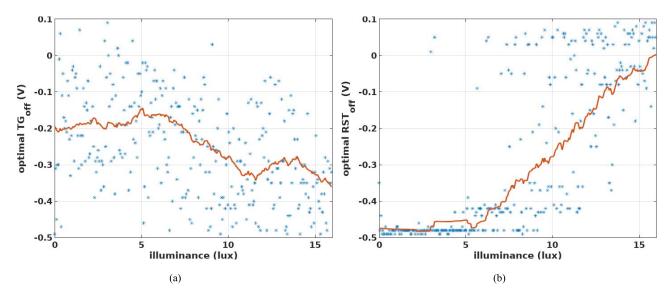

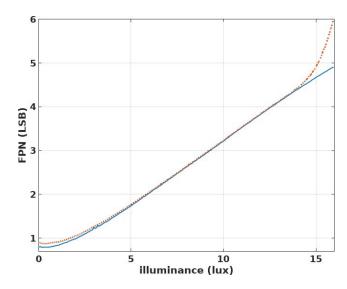

Utilization of the aforementioned Luus–Jaakola algorithm also allows finding optimum values of the voltages  $TG_{OFF}$  and  $RST_{OFF}$  that minimize FPN for the image sensor working at different illumination intensities. (In this case, utilization of the brute force approach is impractical due to the long measurement times required.) The results have been shown in Fig. 9.

Fig. 9. Optimal gate off-voltages of in-pixel transistors as a function of illuminance. (a) Optimal TG<sub>OFF</sub> voltage. (b) Optimal RST<sub>OFF</sub> voltage. Moving average (red line) is shown. The Luus–Jaakola algorithm has been utilized for optimization.

Fig. 10. FPN under illumination of 20 lux.

Fig. 9(a) indicates that the optimum value of the  $TG_{OFF}$  voltage corresponds to a plateau region of FPN (which explains a widespread of the points on the plot). The moving average plot (red line) reveals only slight dependence of  $TG_{OFF}$  on the illumination intensity. Fig. 9(b) shows a strong dependence of the optimum value of the voltage  $RST_{OFF}$  on the illumination intensity. It should be noted that outliers (w.r.t the moving average) in the plot result from finding local minima by the Luus–Jaakola algorithm.

The aforementioned optimization of the control voltages for various illumination intensities may be helpful in identifying physical phenomena that have an effect on DSNU and FPN degradation. In Fig. 9(b), a strong increasing trend of the optimum level of the RST<sub>OFF</sub> voltage can be observed beyond certain illuminance level (5 lux), which may indicate erroneous operation of the imager. This observation allows for finding the root cause of this phenomenon, which is insufficient input common-mode range of the analog comparators in ADCs.

Fig. 11. FPN for optimal  $TG_{OFF}$  and  $RST_{OFF}$  voltages (solid blue line), and for constant (and equal to  $0\ V$ )  $TG_{OFF}$  and  $RST_{OFF}$  voltages (red dotted line).

The above measurements also allowed for a conclusion that the quality of the prototype CIS can be improved using automated adjustment of  $TG_{OFF}$  and  $RST_{OFF}$  depending on illumination intensity. For example, Fig. 10 shows the FPN surface for an illuminance of 15 lux. Based on the measurements obtained using the Luus–Jaakola algorithm, the optimum values of  $TG_{OFF}$  and  $RST_{OFF}$  have been obtained for many illumination levels (without the necessity of plotting the entire FPN surface for each of them). The benefits of the implemented automated voltage adjustment have been shown in Fig. 11.

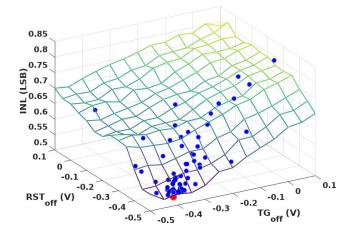

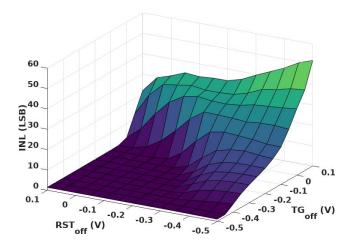

# C. Optimum of INL

As an example of more advanced operations, the measurement of INL is discussed here. INL measurement in the tested CIS has been limited to low illumination conditions (0–1.5 lux)

Fig. 12. INL of the CIS for weak illumination  $(13 \times 13 \text{ grid})$ , an optimization process (blue dots), and the final result of an optimization (red dot). The Luus–Jaakola algorithm has been utilized for optimization.

Fig. 13. INL of the CIS for illumination range 0-16 lux.

in order to illustrate the effect of the leakage currents and other physical phenomena that are difficult to analyze and simulate at the stage of integrated circuit design.

First, a brute force approach has been utilized. The response of the CIS has been measured for 31 illumination levels from 0 to 1.5 lux. A single measurement required acquisition, reading, and processing of 50 image frames. Next, linear regression and calculation of the INL error is performed. Measurements have been repeated for subsequent combinations of  $TG_{OFF}$  and  $RST_{OFF}$ . Having in mind a lengthy measurement procedure, the voltage has been changed with the step of 50 mV. The obtained INL plot (Fig. 12,  $13 \times 13$  grid) one can find the optimum values of  $TG_{OFF}$  and  $RST_{OFF}$ . The complete measurement cycle  $(13 \times 13 \times 31 = 5239$  measurements) took 300 min.

The overall measurement time can be reduced by a factor of three by using Luus–Jaakola optimization. Blue dots in Fig. 12 represent subsequent measurement locations of INL in the course of optimization. The final result (red dot) has been obtained in 67 iterations. Each point represents the measurement of the imager response for 31 illumination levels. In comparison to the brute force approach, optimization reduces the overall number of measurements to  $31 \times 67 =$

2077, and the measurement time to 110 min. Moreover, this method is more accurate because the voltage values are not limited to 50-mV grid.

Fig. 13 shows INL measurements for the illuminance from 0 to 16 lux. The proposed measurement system allows for the fast determination of the optimum operating conditions of the image sensor.

In order to facilitate computations, an additional functionality of the measurement system has been utilized, which is a possibility of communication with the external computing server using the Ethernet interface. Communication has been realized using the NFS file system. A server has been established on the PC machine using the Octave software for computing linear regression and error values.

The user can choose between the following methods: maximum of absolute differences, sum of absolute differences, and sum of squared differences. The server gets the file with the imager response values and returns (in a separate file) the INL value. Based on that value, the measurement system can continue the optimization process. The communication mechanism described above can also be used to implement more involved optimization algorithms (e.g., Bayesian optimization algorithm), which are difficult to implement directly in the measurement system based on the MicroBlaze processor.

#### VI. CONCLUSION

In this paper, a highly efficient platform for prototype CIS measurement has been proposed. The system features solutions accelerating measurements and enabling imagers characterization as well as advanced optimization in a reasonable time. In the developed system, a flat diffuser is applied instead of an integrating sphere. Such equipment is simple and permits reliable characterization of CISs of the DR up to 10 bits. Imagers with higher dynamic can be characterized and optimized using the presented system if an integrating sphere is applied.

# REFERENCES

- [1] J. Nakamura, "Basics of image sensors," in *Image Sensors and Signal Processing for Digital Still Cameras*, J. Nakamura, Ed. Boca Raton, FL, USA: Taylor & Francis, 2006, pp. 53–93.

- [2] J. Yuan, H. Y. Chan, S. W. Fung, and B. Liu, "An activity-triggered 95.3 dB DR 75.6 dB THD CMOS imaging sensor with digital calibration," *IEEE J. Solid-State Circuits*, vol. 44, no. 10, pp. 2834–2843, Oct. 2009.

- [3] A. Lopich and P. Dudek, "A SIMD cellular processor array vision chip with asynchronous processing capabilities," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 58, no. 10, pp. 2420–2431, Oct. 2011.

- [4] S. J. Carey, A. Lopich, D. R. W. Barr, B. Wang, and P. Dudek, "A 100,000 fps vision sensor with embedded 535 GOPS/W 256×256 SIMD processor array," presented at the VLSI Circuits Symp., Kyoto, Japan, 2013, pp. C182–C183.

- [5] W. Jendernalik, G. Blakiewicz, J. Jakusz, S. Szczepanski, and R. Piotrowski, "An analog sub-miliwatt CMOS image sensor with pixellevel convolution processing," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 60, no. 2, pp. 279–289, Feb. 2013.

- [6] M. Klosowski, W. Jendernalik, J. Jakusz, G. Blakiewicz, and S. Szczepanski, "A CMOS pixel with embedded ADC, digital CDS and gain correction capability for massively parallel imaging array," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 64, no. 1, pp. 38–49, Jan. 2017.

- [7] Z. Ignjatovic, D. Maricic, and M. F. Bocko, "Low power, high dynamic range CMOS image sensor employing pixel-level oversampling ΣΔ analog-to-digital conversion," *IEEE Sensors J.*, vol. 12, no. 4, pp. 737–746, Apr. 2012.

- [8] J. Fernández-Berni, R. Carmona-Galán, and L. Carranza-González, "FLIP-Q: A QCIF resolution focal-plane array for low-power image processing," *IEEE J. Solid-State Circuits*, vol. 46, no. 3, pp. 669–680, Mar. 2011.

- [9] A. Elouardi, S. Bouaziz, A. Dupret, L. Lacassagne, J. O. Klein, and R. Reynaud, "Image processing vision systems: Standard image sensors versus retinas," *IEEE Trans. Instrum. Meas.*, vol. 56, no. 5, pp. 1675–1687, Oct. 2007.

- [10] J. Dubois, D. Ginhac, M. Paindavoine, and B. Heyrman, "A 10 000 fps CMOS sensor with massively parallel image processing," *IEEE J. Solid-State Circuits*, vol. 43, no. 3, pp. 706–717, Mar. 2008.

- [11] Z. Lin, M. W. Hoffman, N. Schemm, W. D. León-Salas, and S. Balkir, "A CMOS image sensor for multi-level focal plane image decomposition," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 55, no. 9, pp. 2561–2572, Oct. 2008.

- [12] A. Nilchi, J. Aziz, and R. Genov, "Focal-plane algorithmically-multiplying CMOS computational image sensor," *IEEE J. Solid-State Circuits*, vol. 44, no. 6, pp. 1829–1839, Jun. 2009.

- [13] A. O. Ercan, F. Xiao, X. Liu, S. Lim, A. El Gamal, and B. Wandell, "Experimental high speed CMOS image sensor system and applications," in *Proc. 1st IEEE Int. Conf. Sensors (SENSORS)*, vol. 1. Jun. 2002, pp. 15–20.

- [14] M. Sarkar, D. S. S. Bello, C. van Hoof, and A. J. P. Theuwissen, "Integrated polarization-analyzing CMOS image sensor for detecting the incoming light ray direction," *IEEE Trans. Instrum. Meas.*, vol. 60, no. 8, pp. 2759–2767, Aug. 2011.

- [15] H.-C. Chen, T.-S. Liao, and H.-C. Hwang, "An integrated embedded system for evaluating performance parameters of CMOS image sensor," *IEEE Trans. Instrum. Meas.*, vol. 61, no. 8, pp. 2328–2330, Aug. 2012.

- [16] W. S. Boyle and G. E. Smith, "Charged-coupled devices—A new approach to MIS device structures," *IEEE Spectr.*, vol. 8, no. 7, pp. 18–27, Jul. 1971.

- [17] L. Balmer and J. L. Douce, "An application of hill climbing techniques in measurement," *IEEE Trans. Autom. Control*, vol. AC-27, no. 1, pp. 89–93, Feb. 1982.

- [18] R. Luus and T. H. I. Jaakola, "Optimization by direct search and systematic reduction of the size of search region," AIChE J., vol. 19, no. 4, pp. 760–766, 1973.

M. Kłosowski received the M.Sc. and Ph.D. degrees in electrical engineering from the Gdańsk University of Technology, Gdańsk, Poland, in 1994 and 2001, respectively.

Since 2001, he has been with the Department of Microelectronic Systems, Gdańsk University of Technology. His current research interests include the areas of vision sensors, video processing and applications of field-programmable gate arrays to high-performance computing.

W. Jendernalik received the M.Sc. and Ph.D. degrees in electrical engineering from the Gdańsk University of Technology, Gdańsk, Poland, in 1997 and 2006, respectively.

From 2001 to 2006, he was a Research Assistant with the Department of Electronic Circuits, Gdańsk University of Technology, where he was involved in the field of continuous-time analog filters. Since 2007, he has been an Assistant Professor with the Department of Microelectronic Systems. His current research interests include analog integrated

circuits with emphasis on low-power vision processors and high-frequency analog filters.

**G. Blakiewicz** received the M.Sc., Ph.D., and D.Sc. degrees in electrical engineering from the Gdańsk University of Technology, Gdańsk, Poland, in 1990, 1997, and 2013, respectively.

From 1990 to 1997, he was a Research Assistant with the Department of Electronic Circuits, Gdańsk University of Technology, where he was involved in the field of discrete-time analog filters. Since 1997, he has been an Assistant Professor with the Department of Microelectronic Systems. From 2003 to 2004, he was a Visiting Assistant Professor with the

Electrical Engineering Department, Portland State University, Portland, OR, USA. His current research interests include analog design with emphasis on low voltage, low power, and reduction of sensitivity to substrate noise.

S. Szczepański received the M.Sc. and Ph.D. degrees in electronic engineering from the Gdańsk University of Technology, Gdańsk, Poland, in 1975 and 1986, respectively.

In 1986, he was a Visiting Research Associate with the Institute National Polytechnique de Toulouse, Toulouse, France. From 1990 to 1991, he was with the Department of Electrical Engineering, Portland State University, Portland, OR, USA, on a Kosciuszko Foundation Fellowship. In 1998, he joined as a Visiting Professor with the Faculty of

Engineering and Information Sciences, University of Hertfordshire, Hatfield, U.K. He is currently a Professor with the Department of Microelectronic Systems, Faculty of Electronics, Telecommunications and Informatics, Gdańsk University of Technology. He has authored more than 160 papers and holds three patents. His teaching and current research interests include circuit theory, fully integrated analog filters, high-frequency transconductance amplifiers, and analog integrated circuit design and analog signal processing.

**J. Jakusz** received the M.Sc. and Ph.D. degrees in electrical engineering from the Gdańsk University of Technology, Gdańsk, Poland, in 1990 and 2000, respectively.

From 1990 to 1997, he was a Teaching and Research Assistant with the Department of Electronic Circuits, Gdańsk University of Technology, where he was involved in the field of analog integrated filter design. Since 2000, he has been an Assistant Professor with the Department of Microelectronic Systems. His current research interests

include analog integrated circuits, vision processors, and analog filters.

S. Kozieł (M'03–SM'07) received the M.Sc. and Ph.D. degrees in electronic engineering from the Gdansk University of Technology, Gdansk, Poland, in 1995 and 2000, respectively, and the M.Sc. degree in theoretical physics and mathematics and the Ph.D. degree in mathematics from the University of Gdansk, Gdansk, Poland, in 2000, 2002, and 2003, respectively.

He is currently a Professor with the School of Science and Engineering, Reykjavik University, Reykjavik, Iceland. He is also a Visiting Professor

with the Gdansk University of Technology. His current research interests include CAD and modeling of microwave circuits, simulation-driven design, surrogate-based optimization, space mapping, circuit theory, analog signal processing, evolutionary computation, and numerical analysis.